Краткое описание архитектуры Эльбрус

Гость 27 Июня 2014 в 15:01:02

Работы над архитектурой «Эльбрус» начались в 1986 г. в коллективе Института точной механики и вычислительной техники (ИТМ и ВТ) им. С.А. Лебедева, в котором до этого были созданы советские высокопроизводительные комплексы «Эльбрус-1» и «Эльбрус-2». Разработка вычислительного комплекса «Эльбрус-3», которая велась под руководством Б.А. Бабаяна, была завершена в 1991 г. В этом вычислительном комплексе впервые были воплощены в жизнь идеи явного управления параллелизмом операций с помощью компилятора.

Начавшиеся с 1992 г. экономические изменения в России не позволили разработчикам «Эльбруса-3» завершить наладку комплекса. В том же 1992 г. коллектив разработчиков машин семейства «Эльбрус» выделился в компанию ЗАО «МЦСТ» и начал вести работы над микропроцессорной реализацией архитектуры «Эльбрус».

Архитектура «Эльбрус» - оригинальная российская разработка. Ключевые черты архитектуры «Эльбрус» - энергоэффективность и высокая производительность, достигаемые при помощи задания явного параллелизма операций.

Ключевые особенности архитектуры Эльбрус

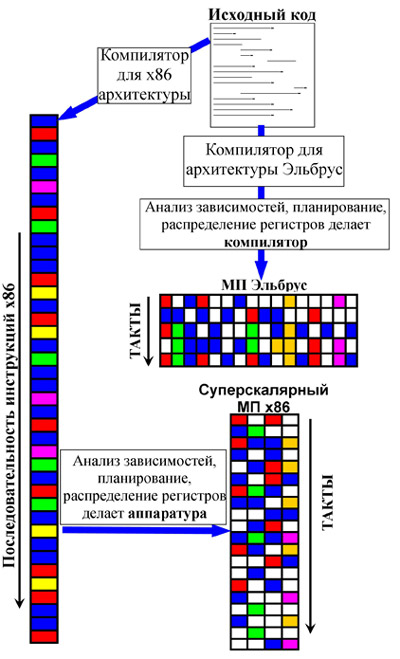

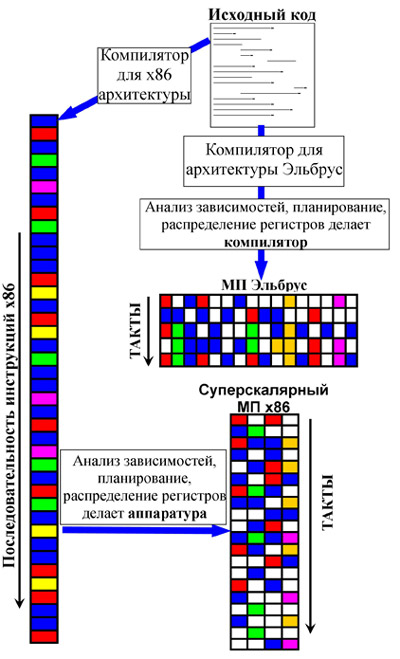

В традиционных архитектурах типа RISC или CISC (х86, PowerPC, SPARC, MIPS, ARM), на вход процессора поступает поток инструкций, которые рассчитаны на последовательное исполнение. Процессор может детектировать независимые операции и запускать их параллельно (суперскалярность) и даже менять их порядок (внеочередное исполнение). Однако динамический анализ зависимостей и поддержка внеочередного исполнения имеет свои ограничения: лучшие современные процессоры способны анализировать и запускать до 4-х команд за такт. Кроме того, соответствующие блоки внутри процессора потребляют заметное количество энергии.

В архитектуре «Эльбрус» основную работу по анализу зависимостей и оптимизации порядка операций берет на себя компилятор. Процессору на вход поступают т.н. «широкие команды», в каждой из которых закодированы инструкции для всех исполнительных устройств процессора, которые должны быть запущены на данном такте. От процессора не требуется анализировать зависимости между операндами или переставлять операции между широкими командами: все это делает компилятор, исходя из анализа исходного кода и планирования ресурсов процессора. В результате аппаратура процессора может быть проще и экономичнее.

Компилятор способен анализировать исходный код гораздо тщательнее, чем аппаратура RISC/CISC процессора, и находить больше независимых операций. Поэтому в архитектуре Эльбрус больше параллельно работающих исполнительных устройств, чем в традиционных архитектурах, и на многих алгоритмах она демонстрирует непревзойденную архитектурную скорость.

Возможности архитектуры Эльбрус:

6 каналов арифметико-логических устройств (АЛУ), работающих параллельно.

Регистровый файл из 256 84-разрядных регистров.

Аппаратная поддержка циклов, в том числе с конвейеризацией. Повышает эффективность использования ресурсов процессора.

Программируемое асинхронное устройство предварительной подкачки данных с отдельными каналами считывания. Позволяет скрыть задержки от доступа к памяти и полнее использовать АЛУ.

Поддержка спекулятивных вычислений и однобитовых предикатов. Позволяет уменьшить число переходов и параллельно исполнять несколько ветвей программы.

Широкая команда, способная при максимальном заполнении задать в одном такте до 23 операций (более 33 операций при упаковке операндов в векторные команды).

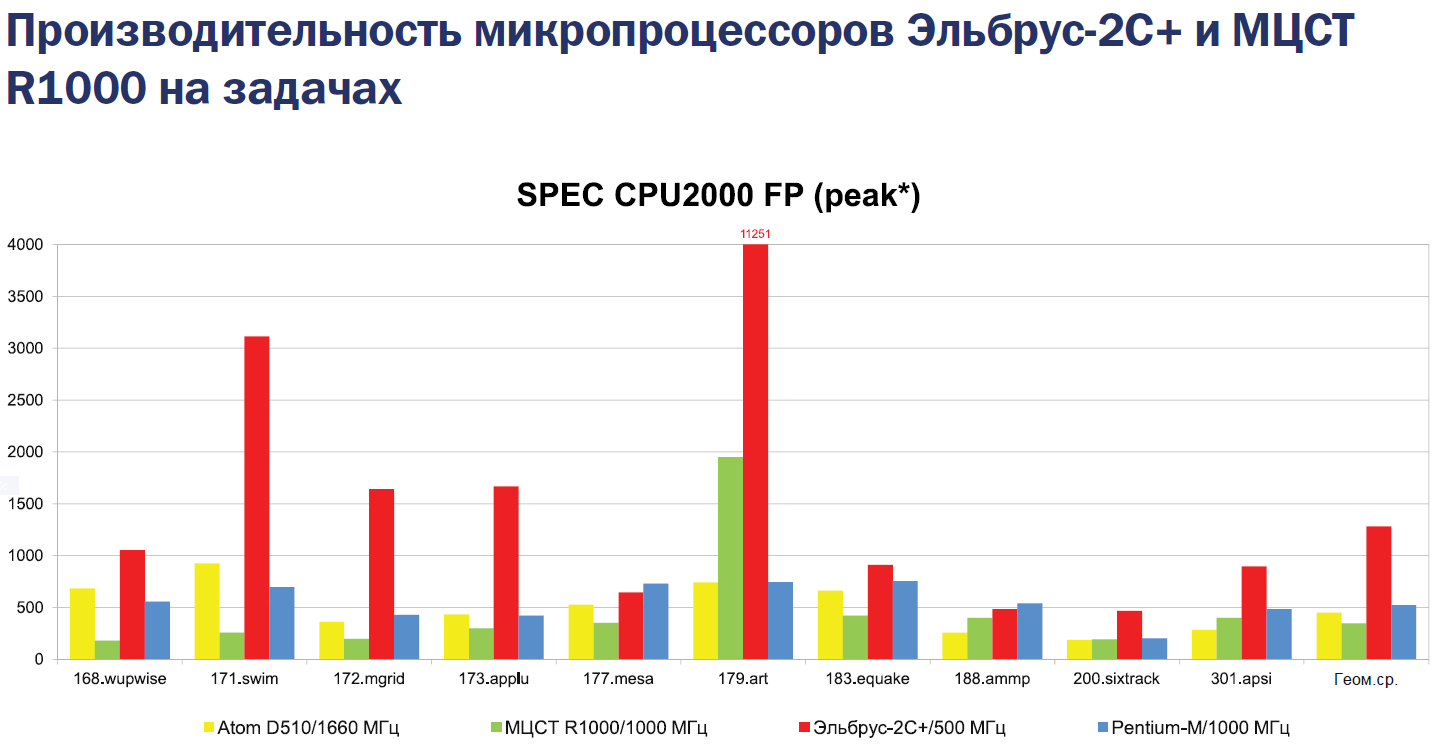

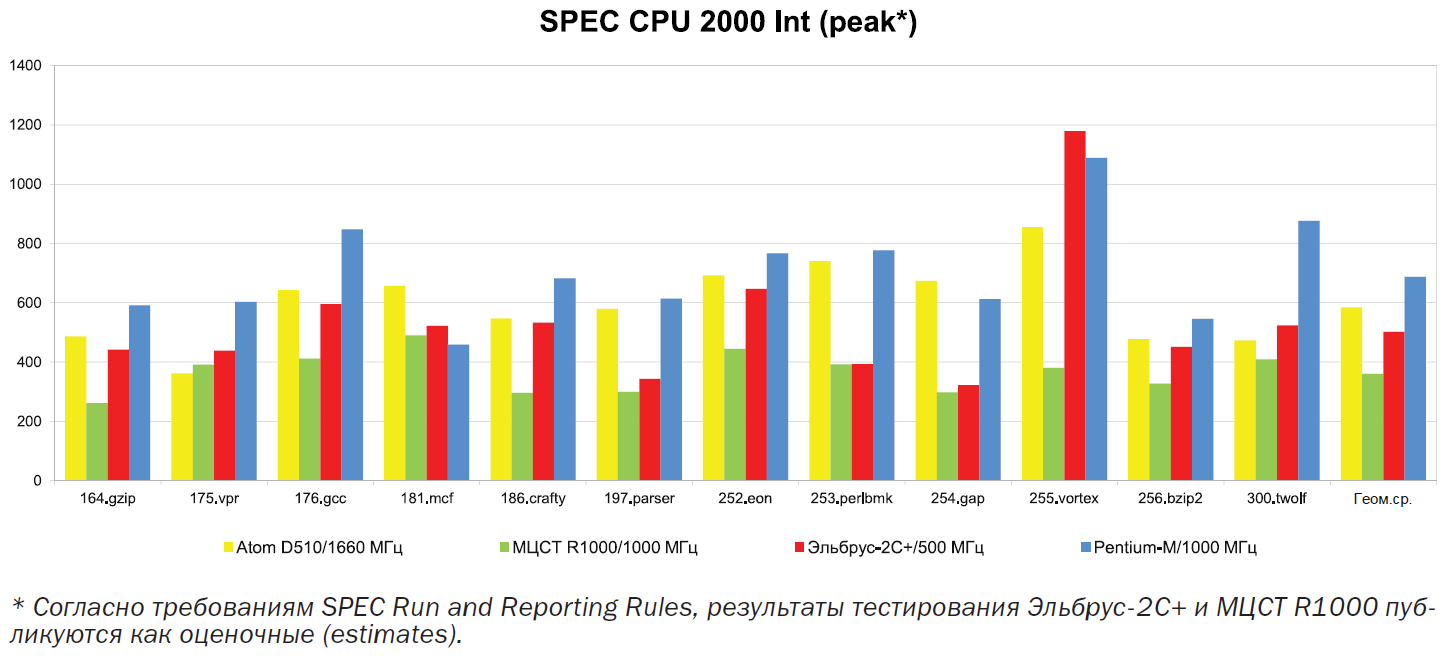

Производительность на реальных задачах:

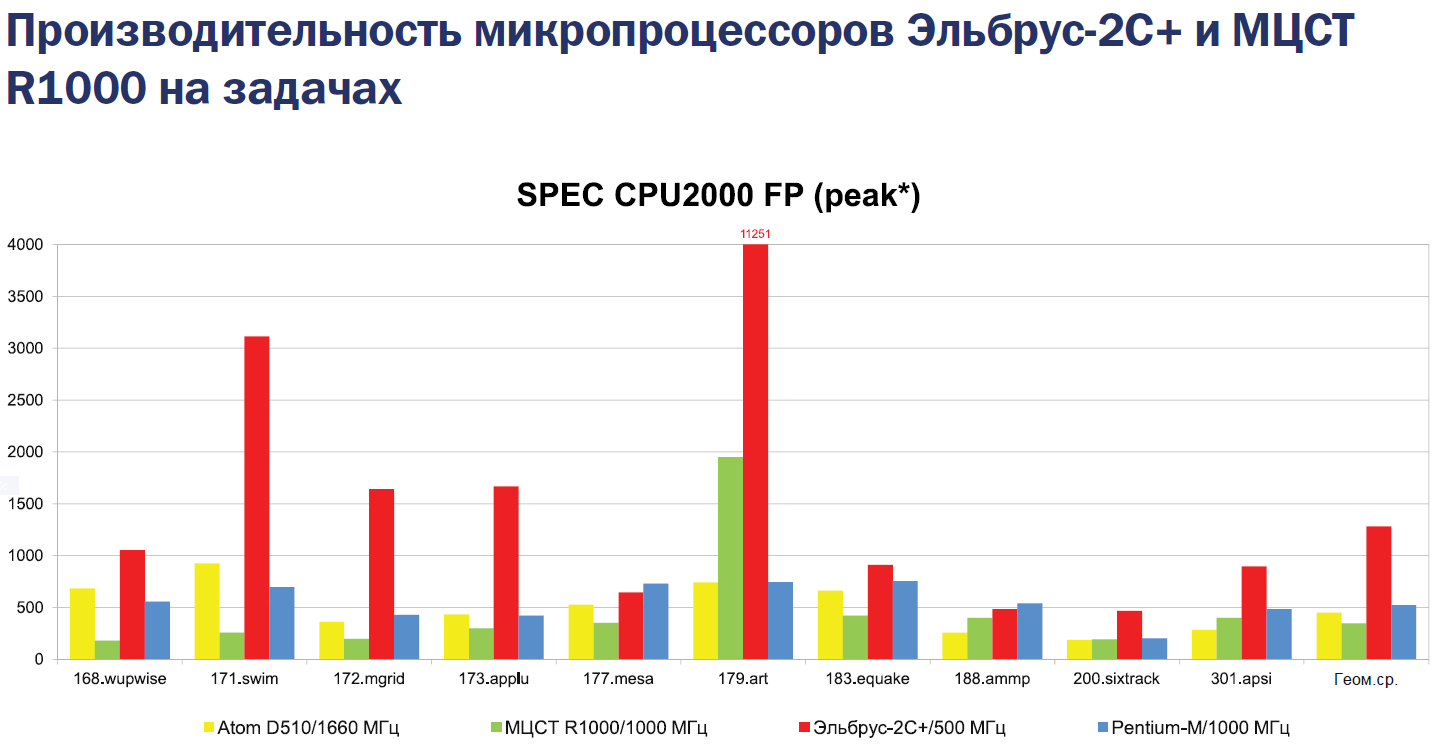

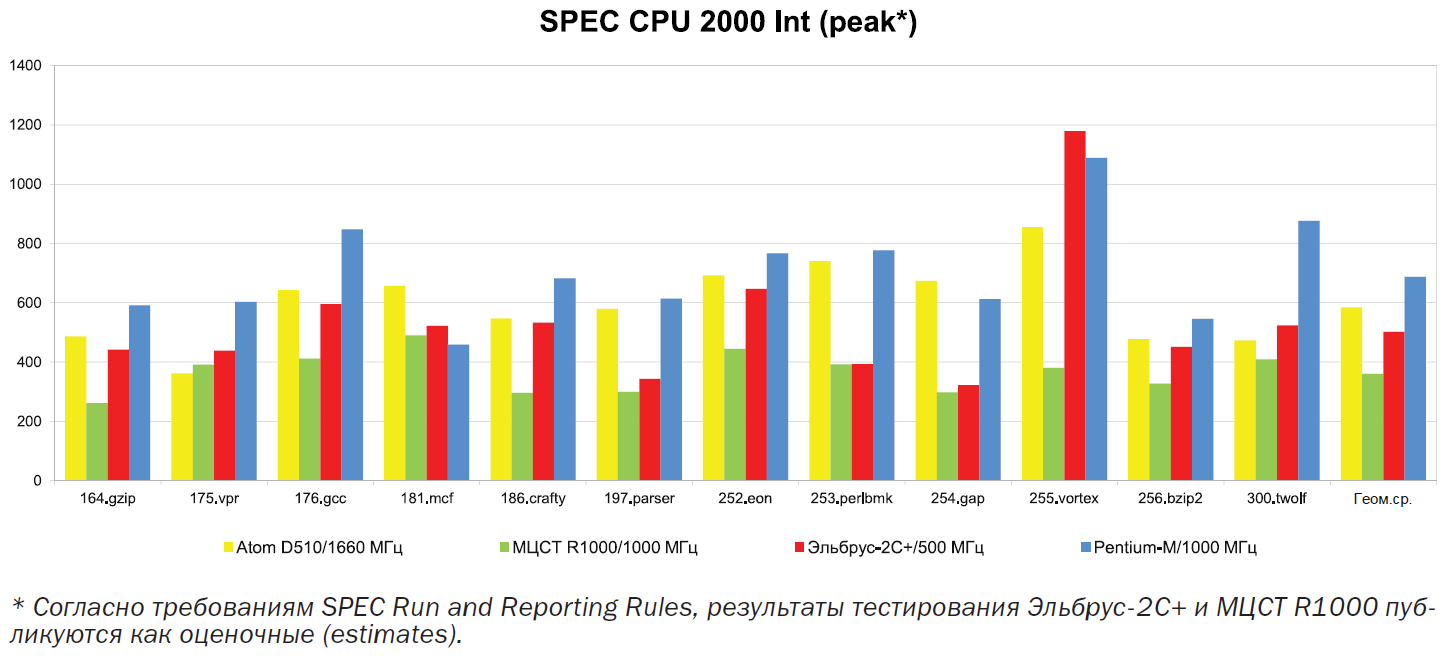

Ниже приведена производительность процессора

Эльбрус-2С+ на задачах из пакета SPEC2000 по сравнению с процессорами Intel Pentium-M ULV (1ГГц, кэш-память 1М, 2хDDR-266) и Intel Atom D510 (1,66 ГГц, кэш-память 1М, DDR2-800).

Данные для Intel Pentium-M ULV получены с сайта spec.org, компилятор ICC 9.1. Для замера производительности процессора Intel Atom D510 использовалась собственная сборка тестов SPEC силами сотрудников МЦСТ.

Важно отметить, что правила комитета SPEC запрещают осуществлять модификацию исходных кодов тестов. Практика показала, что архитектура Эльбрус обладает значительным резервом производительности, который можно задействовать путём модификаций исходного кода в критических участках.

Эмуляция архитектуры х86

Еще на этапе проектирования МП Эльбрус у разработчиков было понимание важности поддержки программного обеспечения, написанного для архитектуры Intel х86. Для этого была реализована система динамической (т.е. в процессе исполнения программы, или «на лету») трансляции двоичных кодов х86 в коды процессора Эльбрус. Фактически, система двоичной трансляции создает виртуальную машину, в которой работает гостевая ОС для архитектуры х86. Благодаря нескольким уровням оптимизации удается достичь высокой скорости работы оттранслированного кода (см. диаграммы выше). Качество эмуляции архитектуры х86 подтверждается успешным запуском на платформе Эльбрус более 20 операционных систем (в том числе несколько версий Windows) и сотен приложений.

Защищенный режим исполнения программ

Одна из самых интересных идей, унаследованных от архитектур Эльбрус-1 и Эльбрус-2 – это так называемое защищенное исполнение программ. Его суть заключается в том, чтобы гарантировать работу программы только с инициализированными данными, проверять все обращения в память на принадлежность к допустимому диапазону адресов, обеспечивать межмодульную защиту (например, защищать вызывающую программу от ошибки в библиотеке). Все эти проверки осуществляются аппаратно. Для защищенного режима имеется полноценный компилятор С/С++ и библиотека run-time поддержки.

Даже в обычном, «незащищенном» режиме работы МП Эльбрус имеются особенности, повышающие надежность системы. Так, стек связующей информации (цепочка адресов возврата при процедурных вызовах) отделен от стека пользовательских данных и недоступен для таких вирусных атак, как подмена адреса возврата. Стоит отдельно отметить, что в настоящее время вирусов для платформы «Эльбрус» просто не существует.

Сфера применения микропроцессоров архитектуры Эльбрус

Расширенный температурный диапазон, возможность локализации производства:

Государственный заказ, промышленные компьютеры, автомобильная электроника

Повышенная защищенность от вирусных атак:

Платежные терминалы, сетевые экраны, взломоустойчивые серверы

Высокая производительность на криптографических алгоритмах:

Модули шифрования, защищенные тонкие клиенты, прочие системы безопасности

Высокая производительность на вычислениях с действительными числами (float, double):

Робототехника, авионика, промышленные контроллеры, системы обработки изображений, суперкомпьютеры

Работа под управлением бинарного компилятора в режиме совместимости с архитектурой х86:

Интернет-терминалы, маломощные рабочие станции, малогабаритные настольные и встраиваемые компьютеры

Защищенный режим:

Особо ответственные системы, отладочные стенды

Любое упоминание зарегистрированных торговых марок производится только для целей идентификации. Вышеупомянутые зарегистрированные торговые марки являются собственностью соответствующих частных владельцев и корпораций.

Источник: http://www.mcst.ru/2-3.htm

Начавшиеся с 1992 г. экономические изменения в России не позволили разработчикам «Эльбруса-3» завершить наладку комплекса. В том же 1992 г. коллектив разработчиков машин семейства «Эльбрус» выделился в компанию ЗАО «МЦСТ» и начал вести работы над микропроцессорной реализацией архитектуры «Эльбрус».

Архитектура «Эльбрус» - оригинальная российская разработка. Ключевые черты архитектуры «Эльбрус» - энергоэффективность и высокая производительность, достигаемые при помощи задания явного параллелизма операций.

Ключевые особенности архитектуры Эльбрус

В традиционных архитектурах типа RISC или CISC (х86, PowerPC, SPARC, MIPS, ARM), на вход процессора поступает поток инструкций, которые рассчитаны на последовательное исполнение. Процессор может детектировать независимые операции и запускать их параллельно (суперскалярность) и даже менять их порядок (внеочередное исполнение). Однако динамический анализ зависимостей и поддержка внеочередного исполнения имеет свои ограничения: лучшие современные процессоры способны анализировать и запускать до 4-х команд за такт. Кроме того, соответствующие блоки внутри процессора потребляют заметное количество энергии.

В архитектуре «Эльбрус» основную работу по анализу зависимостей и оптимизации порядка операций берет на себя компилятор. Процессору на вход поступают т.н. «широкие команды», в каждой из которых закодированы инструкции для всех исполнительных устройств процессора, которые должны быть запущены на данном такте. От процессора не требуется анализировать зависимости между операндами или переставлять операции между широкими командами: все это делает компилятор, исходя из анализа исходного кода и планирования ресурсов процессора. В результате аппаратура процессора может быть проще и экономичнее.

Компилятор способен анализировать исходный код гораздо тщательнее, чем аппаратура RISC/CISC процессора, и находить больше независимых операций. Поэтому в архитектуре Эльбрус больше параллельно работающих исполнительных устройств, чем в традиционных архитектурах, и на многих алгоритмах она демонстрирует непревзойденную архитектурную скорость.

Возможности архитектуры Эльбрус:

6 каналов арифметико-логических устройств (АЛУ), работающих параллельно.

Регистровый файл из 256 84-разрядных регистров.

Аппаратная поддержка циклов, в том числе с конвейеризацией. Повышает эффективность использования ресурсов процессора.

Программируемое асинхронное устройство предварительной подкачки данных с отдельными каналами считывания. Позволяет скрыть задержки от доступа к памяти и полнее использовать АЛУ.

Поддержка спекулятивных вычислений и однобитовых предикатов. Позволяет уменьшить число переходов и параллельно исполнять несколько ветвей программы.

Широкая команда, способная при максимальном заполнении задать в одном такте до 23 операций (более 33 операций при упаковке операндов в векторные команды).

Производительность на реальных задачах:

Ниже приведена производительность процессора

Эльбрус-2С+ на задачах из пакета SPEC2000 по сравнению с процессорами Intel Pentium-M ULV (1ГГц, кэш-память 1М, 2хDDR-266) и Intel Atom D510 (1,66 ГГц, кэш-память 1М, DDR2-800).

Данные для Intel Pentium-M ULV получены с сайта spec.org, компилятор ICC 9.1. Для замера производительности процессора Intel Atom D510 использовалась собственная сборка тестов SPEC силами сотрудников МЦСТ.

Важно отметить, что правила комитета SPEC запрещают осуществлять модификацию исходных кодов тестов. Практика показала, что архитектура Эльбрус обладает значительным резервом производительности, который можно задействовать путём модификаций исходного кода в критических участках.

Эмуляция архитектуры х86

Еще на этапе проектирования МП Эльбрус у разработчиков было понимание важности поддержки программного обеспечения, написанного для архитектуры Intel х86. Для этого была реализована система динамической (т.е. в процессе исполнения программы, или «на лету») трансляции двоичных кодов х86 в коды процессора Эльбрус. Фактически, система двоичной трансляции создает виртуальную машину, в которой работает гостевая ОС для архитектуры х86. Благодаря нескольким уровням оптимизации удается достичь высокой скорости работы оттранслированного кода (см. диаграммы выше). Качество эмуляции архитектуры х86 подтверждается успешным запуском на платформе Эльбрус более 20 операционных систем (в том числе несколько версий Windows) и сотен приложений.

Защищенный режим исполнения программ

Одна из самых интересных идей, унаследованных от архитектур Эльбрус-1 и Эльбрус-2 – это так называемое защищенное исполнение программ. Его суть заключается в том, чтобы гарантировать работу программы только с инициализированными данными, проверять все обращения в память на принадлежность к допустимому диапазону адресов, обеспечивать межмодульную защиту (например, защищать вызывающую программу от ошибки в библиотеке). Все эти проверки осуществляются аппаратно. Для защищенного режима имеется полноценный компилятор С/С++ и библиотека run-time поддержки.

Даже в обычном, «незащищенном» режиме работы МП Эльбрус имеются особенности, повышающие надежность системы. Так, стек связующей информации (цепочка адресов возврата при процедурных вызовах) отделен от стека пользовательских данных и недоступен для таких вирусных атак, как подмена адреса возврата. Стоит отдельно отметить, что в настоящее время вирусов для платформы «Эльбрус» просто не существует.

Сфера применения микропроцессоров архитектуры Эльбрус

Расширенный температурный диапазон, возможность локализации производства:

Государственный заказ, промышленные компьютеры, автомобильная электроника

Повышенная защищенность от вирусных атак:

Платежные терминалы, сетевые экраны, взломоустойчивые серверы

Высокая производительность на криптографических алгоритмах:

Модули шифрования, защищенные тонкие клиенты, прочие системы безопасности

Высокая производительность на вычислениях с действительными числами (float, double):

Робототехника, авионика, промышленные контроллеры, системы обработки изображений, суперкомпьютеры

Работа под управлением бинарного компилятора в режиме совместимости с архитектурой х86:

Интернет-терминалы, маломощные рабочие станции, малогабаритные настольные и встраиваемые компьютеры

Защищенный режим:

Особо ответственные системы, отладочные стенды

Любое упоминание зарегистрированных торговых марок производится только для целей идентификации. Вышеупомянутые зарегистрированные торговые марки являются собственностью соответствующих частных владельцев и корпораций.

Источник: http://www.mcst.ru/2-3.htm

|

|

|

Добавить новость

Добавить новость

Шрифт:

Шрифт: